# Mixing Multi-Core CPUs and GPUs for Scientific Simulation Software

K.A. HAWICK, A. LEIST AND D.P. PLAYNE

Computer Science Institute of Information & Mathematical Sciences Massey University at Albany, Auckland, New Zealand Email: {k.a.hawick | a.leist | d.p.playne}@massey.ac.nz

Recent technological and economic developments have led to widespread availability of multi-core CPUs and specialist accelerator processors such as graphical processing units (GPUs). The accelerated computational performance possible from these devices can be very high for some applications paradigms. Software languages and systems such as NVIDIA's CUDA and Khronos consortium's open compute language (OpenCL) support a number of individual parallel application programming paradigms. To scale up the performance of some complex systems simulations, a hybrid of multi-core CPUs for coarse-grained parallelism and very many core GPUs for data parallelism is necessary. We describe our use of hybrid applications using threading approaches and multi-core CPUs to control independent GPU devices. We present speed-up data and discuss multi-threading software issues for the applications level programmer and offer some suggested areas for language development and integration between coarse-grained and fine-grained multi-thread systems. We discuss results from three common simulation algorithmic areas including: partial differential equations; graph cluster metric calculations and random number generation. We report on programming experiences and selected performance for these algorithms on: single and multiple GPUs; multi-core CPUs; a CellBE; and using OpenCL. We discuss programmer usability issues and the outlook and trends in multi-core programming for scientific applications developers.

**Keywords:** multi-core; accelerators; GPU; CUDA; CellBE; OpenCL; data parallelism; thread model.

## Contents

| Intr | roduction                       |

|------|---------------------------------|

| 1.1  | Multi-Core Processing           |

|      | Re-embracing Parallelism        |

|      | Article Organisation            |

| Rev  | view of Accelerator Platforms   |

| 2.1  | Multi-Core CPU                  |

| 2.2  | Graphical Processing Units      |

|      | 2.2.1 NVIDIA Tesla Architecture |

|      | 2.2.2 NVIDIA Tesla Memory       |

|      | 2.2.3 CUDA Threads              |

|      | 2.2.4 Multi-GPU                 |

|      | 2.2.5 GPU-Accelerated Clusters  |

| 2.3  | Cell Broadband Engine           |

| 2.4  | Other Hardware Approaches       |

| <b>4</b> | $\mathbf{Fin}$ | ite Differencing                      | <b>39</b> |

|----------|----------------|---------------------------------------|-----------|

|          | 4.1            | Neighbour Operations                  | 39        |

|          | 4.2            | CPU - Sequential Algorithm            | 39        |

|          | 4.3            | Multi-Core: POSIX Threads             | 40        |

|          | 4.4            | Multi-Core: Threading Building Blocks | 40        |

|          | 4.5            | GPU - CUDA                            | 42        |

|          | 4.6            | Multi-GPU - CUDA & POSIX Threads      | 43        |

|          | 4.7            | OpenCL                                | 44        |

|          | 4.8            | Cell Processor - PS3                  | 46        |

|          | 4.9            | Finite Difference Results             | 46        |

| <b>5</b> | Nev            | wman's Clustering Coefficient         | 48        |

|          | 5.1            | CPU - Sequential Algorithm            | 48        |

|          | 5.2            | Multi-Core: POSIX Threads             | 49        |

|          | 5.3            | Multi-Core: Threading Building Blocks | 49        |

|          | 5.4            | GPU - CUDA                            | 50        |

|          | 5.5            | Multi-GPU - CUDA & POSIX Threads      | 52        |

|          | 5.6            | Cell Processor - PS3                  | 54        |

|          | 5.7            | Clustering Coefficient Results        | 56        |

| 6        | Rar            | ndom Number Generators                | 61        |

|          | 6.1            | CPU - Sequential Algorithm            | 62        |

|          | 6.2            | Multi-Core: POSIX Threads             | 63        |

|          | 6.3            | Multi-Core: Threading Building Blocks | 63        |

|          | 6.4            | GPU - CUDA                            | 64        |

|          | 6.5            | Multi-GPU - CUDA & POSIX Threads      | 66        |

|          | 6.6            | Cell Processor - PS3                  | 66        |

|          | 6.7            | RNG Implementation Results            | 66        |

| 7        | Dis            | cussion                               | 68        |

|          | 7.1            | Accelerator Models                    | 68        |

|          | 7.2            | Model Unification                     | 69        |

|          | 7.3            | Need for a Common Terminology         | 70        |

| 8        | Sun            | nmary and Conclusions                 | 71        |

## 1 Introduction

Power consumption and physical size constraints have led to a "slowing down of Moore's Law" [1,2] for processing devices, in this, the first decade of the millennium. A major consequence is that parallel computing techniques – such as incorporating multiple processing cores and other acceleration technologies – are increasing in importance [3] both for high performance computing systems but also for game machines, desktop and medium-range computing systems. This is an exciting time for parallel computing but there are some as yet unsolved challenges to be addressed for parallel applications programmers to be able to fully exploit multi-core and many-core computing devices [4,5].

In this article we consider the challenge of using current and emerging multi- and many-core accelerator processing devices for application in scientific simulations. We consider three algorithmic areas we believe are representative of this applications area – solving partial differential equations with finite differencing techniques; analysis algorithms for measuring complex networks; and pseudo-random number generation. These areas are not only relevant for typical high performance simulations but are also highly relevant to computer games and other virtual reality simulations which are important economic drivers for the accelerator device technology market.

We are particularly interested in numerical algorithms, for which a road map of ideas and developments is emerging [6]. In the course of our group's research on complex systems and simulations [7,8] we have identified a number of scientific application paradigms such as those based on particles, field models [9], and on graph network representations [10]. The use of accelerators for the paradigm of N-Body particle simulation [11] has been well reported in the literature already [12,13].

Other areas of relevance we have studied but do not have space to report on in this present article include: traditional models of phase transitions such as the Ising model [14] and the use of accelerated supercomputers for studying large simulated systems; uses of accelerators and multicore devices for computational finance Monte Carlo Finance [15, 16]; and other Monte Carlo applications such as generating networks and measuring their properties [17]. Many of these are potentially hybrid applications that do not fit a single program model paradigm but which need the full performance available from processors and any associated accelerators.

#### 1.1 Multi-Core Processing

In recent years there has been a steady increase in the number of processing cores available on a modern processor chip. Dual core systems are now the norm at the time of writing and quad core systems are already becoming economically viable. Hardware vendors have announced and promised economically affordable six and eight core conventional CPU systems and it seems likely this trend will continue. However with increasing concerns over computer power consumption, physical constraints on power dissipation and approaching spatial limitations on present chip electronics fabrication technology there has been a perceptible "slowing down of Moore's law" at least in terms of conventional approaches using uniform and monolithic core designs.

However, some of the most exciting recent accelerated approaches to improving processor performance include use of much larger numbers of simpler specialist processing cores as accelerator supplements to the main processor or processing core. One particularly noteworthy approach is the use of Graphical Processing Units (GPUs) with **very many** cores and which can be used as high performance computing devices in their own right, accelerating computations orchestrated by a conventional CPU program. Another exciting approach is that of CPU designs with more than one core design on a chip. This approach is embodied by the Sony/Toshiba/IBM (STI) consortium's Cell Broadband Engine (CellBE) processor design with its conventional PowerPC main core(PPE) supplemented by eight Synergistic Processing Element(SPE) or auxiliary cores.

Graphical Processing Units [18] are an attractive platform for optimising the speed of a number of application paradigms relevant to the games and computer-generated character animation industries [19]. Chip manufacturers have been successful in incorporating ideas in parallel programming into their family of CPUs, but for backwards compatibility reasons it has not been trivial to make similar major advances with complex CPU chips. The concept of the GPU as a separate accelerator with fewer legacy constraints is one explanation for the recent dramatic improvements in the use of parallel hardware and ideas at a chip level.

GPUs can be used for many parallel applications in addition to their originally intended purpose of graphics processing algorithms. Relatively recent innovations in high-level programming language support and accessibility have caused the wider applications programming community to consider using GPUs in this way [20–22]. The term general-purpose GPU programming (GPGPU) [19] has been adopted to describe this rapidly growing applications level use of GPU hardware.

We explore some detailed coding techniques and performance optimisation techniques offered by the Compute Unified Device Architecture (CUDA) [22] GPU programming language. NVIDIA's CUDA has emerged within the last year as one of the leading programmer tools for exploiting GPUs. It is not the only one [23–26], and inevitably it builds on many past important ideas, concepts and discoveries in parallel computing.

### 1.2 Re-embracing Parallelism

Many of the data-parallel ideas currently in vogue for many-core devices such as GPUs are not new but owe their origins to important massively parallel and data-parallel supercomputer architectures such as the AMT DAP [27] and the Thinking Machines Connection Machine [28, 29]. There have been successful attempts at portable embodiments of data-parallel computing ideas into software libraries, kernels [30,31] and programming languages [32–35]. Much of this software still exists and is used, but was perhaps somewhat overshadowed by the subsequent era of coarser-grained multiprocessor computer systems – perhaps best embodied by cluster computers, and also by software to exploit them such as message-passing systems like MPI [36]. We have since seen some blending together of these ideas in software languages and systems like OpenMP [37]. Interestingly these ideas too are also finding their way onto multi-core devices and can also be used in the context of multiple accelerator devices including GPUs, CellBE, and other multi-core processors.

The economics of mass production and consumer demand for faster desktops and computer games machines means that the high performance computing market is also strongly driven by these devices. There are many possibilities for combining multiple devices and for building hybrid computing systems that can effectively ride the market forces to attain good processing costs for scientific application areas. This however means that in addition to the challenges of programming individual devices, there are also challenges in devising software models to combine them together effectively into clusters and supercomputers [38, 39].

We are interested in how an application programmer makes use of the processing power of these devices and how standards and architectural models will evolve to make this programming effort easier in the future. In this article we use our three applications areas to explore the use of threading and master/slave accelerator device control software architectures for making use of: single and multiple GPUs; CellBEs; and of course conventional multi-core CPUs for purposes of comparison.

### 1.3 Article Organisation

We report on programming fragments and experiences in terms of ease of programming as well as performance analysis. We consider high-level optimisations for individual cores - such as the SIMD and vector instructions, as well as multi-threading approaches to MIMD parallelism. In addition to Intel's Threading Building Block (TBB) system; NVIDIA's Compute Unified Device Architecture (CUDA) and conventional approaches such as PThreads, we report on some preliminary work with the Open Compute Language (OpenCL).

In Section 2 we review some of the important ideas and systems currently prevalent for accelerator device approaches to parallel computing, and in particular we discuss: multi-core CPU issues (Section 2.1); GPU programming architecture ideas (Section 2.2); Multi-GPU issues (Section 2.2.4) and CellBE related issues in Section 2.3.

We report on detailed algorithmic and programming development work in Section 3 where we focus on three broad applications areas: solving regular partial differential equations (Section 4); computing clustering coefficients for complex graph networks (Section 5); and pseudo random number generation (Section 6). We provide some specific code and pseudo-code fragments and implementation ideas as well as performance data on various devices. In Section 7 we discuss some of the overall issues for programming accelerator devices and hybrid system solutions and we offer some tentative conclusions concerning the future of unifying software models like OpenCL in Section 8.

### 2 Review of Accelerator Platforms

The concept of accelerating a (central) processor's performance with a specialist device is not a new one. Two interesting examples of this approach within living memory are the 8087 FPU

floating point accelerator chip used by the Intel 8086 microprocessor to accelerate floating point calculations; and the use of specialist array processors such as the original ICL Distributed Array Processor (DAP) which was in effect a multi-processor accelerator for a conventional mainframe.

Present use of additional processor cores can take the form of: completely separate chips such as GPUs that can contain very many specialist cores and are not dissimilar to the DAP SIMD approach in architecture; the addition of uniform extra cores within the existing main CPU, such as the Intel and AMD and other mainstream CPU vendor approaches; or the form of non-uniform accelerating cores supplementing a conventional core such as the case of the synergistic processing elements (SPEs) in the Sony/Toshiba/IBM Cell Broadband Engine.

As we discuss in this paper all these approaches have merit and can produce very good performance results - but they are all different architecturally and unfortunately need to be programmed differently at an applications level. This is a significant obstacle to applications programmers being able to gain optimal device performance. Therefore in addition to considering the details of the hardware solutions that are emerging in the field of performance accelerators, it is also very interesting to review some of the detailed approaches that are emerging in hardware and in software tools to program such devices, and also how to integrate together hybrid solutions and unify ideas into a common model.

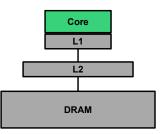

Figure 1: Single-Core CPU Architecture, against which many applications programmers optimise their software.

Figure 1 shows what has become the standard model architecture for nodes and for which target model much present software is optimised. It is useful to contrast this with architectural models that applications programmers must be aware of for the accelerator platforms we discuss below.

We review some specifics on: multi-core CPUs (Section 2.1); GPUs (Section 2.2); use of multiple GPUs (Section 2.2.4); the STI Cell Broadband Engine (Section 2.3) and some other approaches such as the use of reconfigurable hardware accelerator devices such as field programmable gate arrays (FPGAs) in Section 2.4.

### 2.1 Multi-Core CPU

Todays multi-core CPUs make it necessary to re-think the way we develop applications software [40]. New hardware generations do not come with significantly higher clock frequencies like they used to in the past, but instead give us more processing cores that can be used concurrently. In fact it is necessary for applications programmers to explicitly use concurrency to attain anything even close to the peak performance of modern processors. To make use of all the available processing power for computationally intensive tasks, the tasks need to be split up into sub-tasks, which can then be executed on different cores. There are a number of different approaches to parallel programming for multi-core CPUs, ranging from low-level multi-tasking or multi-threading, over high level libraries that provide certain abstractions and features that attempt to simplify concurrent software development, to programming languages or language extensions that have been developed specifically with concurrency in mind [41, 42].

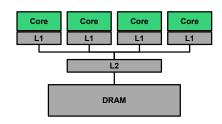

Figure 2: Multi-Core CPU Architecture, four cores with their own L1 caches and a shared L2 cache.

The explicit use of system-threads may have the highest performance potential, but it can be a complex task. It is often not easy to keep all processing cores equally utilised and to keep the overhead introduced by thread management and possible inter-thread communication to a minimum. A low-level threading library, for example the POSIX Thread (PThread) library [43], provides an API for creating and manipulating such platform-dependent threads.

A higher level approach to parallelising computationally intensive work that takes care of some of the tasks that the developer would otherwise have to deal with is the use of a parallel library like the Intel<sup>®</sup> Threading Building Blocks (TBB). This particular C++ library automatically maps logical parallelism onto low-level threads. It emphasises data-parallel programming, executing different parts of a collection on multiple threads using a task scheduler to distribute the work and keep all the processing cores busy. Like the C++ Standard Template Library (STL), TBB makes extensive use of generic programming.

TBB makes it relatively easy to execute loops whose iterations are independent from one another in parallel, invoke functions concurrently, or create and run parallel tasks. It also provides a number of concurrent containers (hash map, queue, vector), different mutex types, atomic operations, as well as scalable memory allocators to name just a few of TBB's features [44].

Some programming languages come with language-level features for concurrent programming. Java [45], for example, has the **synchronized** keyword which enforces mutually exclusive access to blocks of code. Erlang [41], on the other hand, provides language-level features for creating and managing processes and uses message passing for inter-process communication, thus avoiding the need for locks.

### 2.2 Graphical Processing Units

In recent years GPUs have emerged as one of the most favourable and popular accelerator devices available. These GPUs were originally developed to keep up with the increasing demands of the gaming industry which requires them to render increasingly detailed, high-quality computer graphics in real time. As the demands of the computer games increased faster than processor clock speeds, GPU developers adopted the multi-core architectures currently emerging in modern CPU design to keep up with requirements. Over time these GPUs have developed into more general, highly-parallel, many-core processing architectures. A typical high-range GPU contains between 128-480 processors (as compared the the 1-4 cores generally available in CPUs).

As these GPU architectures have moved towards more general processing designs, a number of libraries have been developed that allow users to write non-graphics applications that are computed on GPUs. This is known as General Purpose computation on GPUs or GPGPU. The development of GPGPU libraries such as NVIDIA's CUDA [46], BrookGPU [23], ATI's Stream SDK [47] and sh [25] have made GPGPU applications increasingly easy to develop. They allow developers to implement GPGPU applications in a C-style language. The libraries act as extensions to the C language and handle the interaction between the host CPU and the GPU.

GPUs are very effective at accelerating a wide range of scientific applications. The performance

benefits they offer depends on the application's suitability for parallel decomposition. Much of the research into computer science over the last several decades has been focused on developing methods for parallelising applications. Thus there exist many well-known methods for decomposing applications onto the parallel GPU architecture.

GPUs have data-parallel architectures reminiscent of parallel computers from the 80's such as the DAP [48,49] and the CM [28]. As most of the parallel computing research over the last decade has been focused on developing applications for distributed architectures (i.e. cluster and grid computers). A certain degree of adaptation is required to transfer those parallel designs to the data-parallel architecture of GPUs. Most of the research into GPU programming involves finding the optimal way to solve a problem on the data-parallel architecture while making the best use of the optimisations specific to the GPU architectures.

One of the most inviting features of the GPU is the ease of accessibility. GPUs are relatively cheap and provide easy access to a highly-parallel architecture. This along with easy to use GPGPU APIs allow a large user-base access to high-power parallel applications with little start-up cost. Their computing power to cost ratio is also highly desirable, a \$250 (US) graphics card has the potential to provide over 100x speed-up over a conventional single-core CPU [8].

#### 2.2.1 NVIDIA Tesla Architecture

Of the many GPGPU APIs available [23, 25, 46, 47], NVIDIA's CUDA stands out as the most developed and advanced API. As this library has been developed by NVIDIA, it only operates on NVIDIA GPUs. Our development of GPGPU applications uses this CUDA API and is thus limited to NVIDIA graphics cards. While we specifically discuss the NVIDIA Tesla architecture, ATI's GPU architecture is very similar and many concepts are transferable between the two vendors' products.

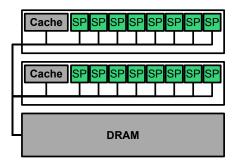

Tesla architecture GPUs contain a scalable array of multi-threaded processing units known as Streaming Multiprocessors (SMs). These SMs each contain eight Scalar Processor (SP) cores which execute the actual instructions. Each SM can perform computation independently but the SP cores within single multiprocessor all execute instructions synchronously. NVIDIA call this paradigm SIMT or Single Instruction Multiple Thread [46].

Figure 3: A Tesla architecture GPU with two Streaming Multiprocessors each containing eight Scalar Processors. This architecture can be easily extended to contain many more multi-processors.

Figure 3 emphasises the hierarchical nature of the multi-processors and cores in the Tesla architecture. This architecture is designed to support a very fine-grained parallelism. GPU applications perform best when split into many threads, each of which performs some smallest unit of work. For example, image processing tasks can be split by assigning one thread for each pixel. As the management, scheduling and execution of threads on the processor cores is performed in hardware on the GPU, managing a large number of threads presents no additional overhead [46].

#### 2.2.2 NVIDIA Tesla Memory

Tesla GPUs contain several different types of memory. As there is no implicit caching on GPUs, memory access can be the limiting factor for many GPU applications. CPUs contain several levels of implicit caching to provide the best memory access speeds possible. GPUs do not contain nearly the same level of memory caches, instead they provide smaller, explicitly accessible caching methods (see Figure 3 as compared to Figure 1 for a comparison between the two architectures). The GPU memory types accessible from CUDA are as follows [46]:

- **Registers** Used to store the local variables belonging to each thread. Provided there are at least 192 active threads, the access time for registers is effectively zero extra clock cycles. If the registers cannot store all the local variables for the threads, Local Memory is used. Stored on-chip.

- Local Memory Actually stored in Global memory, used to store any local variables that cannot fit into the registers. Access times are the same as Global memory. Stored on-device.

- Global Memory The largest section of memory. Only memory type that the CPU can read from and write to. Accessible by all threads, also has the slowest access times (400-600 clock cycles). Total transaction time can be improved by coalescing 16 sequential threads that access 16 sequential and word-aligned memory addresses can coalesce the read/write into a single memory transaction. Stored on-device.

- Shared Memory Read/Write memory that can be used to share data between threads executing on the same multiprocessor (i.e. in the same block). Provided that the threads access different memory banks, the memory transactions are as fast as reading from a register. Stored on-chip.

- **Texture Memory** Cached method of accessing Global memory. Global memory bound to a texture will only be read if the desired value is not already stored in the cache. If so the cache is reloaded with that value and the values surrounding it in the spatiality defined by the texture dimensions. On a cache hit, the transaction is as fast as reading from registers. Stored on-chip.

- **Constant Memory** Another cached method of accessing Global memory, a Global memory read is only required in the event of a cache miss. If all threads read the same value from constant memory, the cost is the same as reading from registers. Stored on-chip.

As these different types of memory must be used explicitly by the developer, a great deal more consideration of memory access is required when developing a GPU application as compared to a CPU implementation. Correct use of these memory types is vital to the performance of a GPU application [8]. Correct use is not limited to the type of memory use but also the access patterns and thread block arrangements. The memory access patterns are dependent on the organisation of threads into blocks and thus decisions about block sizes and shapes must be carefully considered.

#### 2.2.3 CUDA Threads

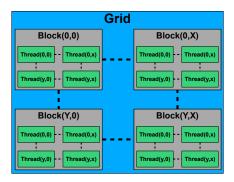

When developing a CUDA application, the algorithm must be decomposed into a number of SIMT threads. The actual scheduling, management and execution of these threads is performed by the GPU itself but a certain degree of control is still available to the developer. A CUDA application has a number of threads organised into blocks, which are all arranged into a grid (See Figure 4). A block of threads has three dimensions (x,y,z) and can contain no more than  $2^9$  threads. A grid has two dimensions (x,y) and has a maximum size of  $2^{16}$  in each dimension. CUDA allows the user to control the arrangement of threads into blocks and the blocks into the grid. The developer can control how these threads are arranged in order to make optimal use of the on-chip memory in

Figure 4: The hierarchy of CUDA threads, this grid contains (X, Y) blocks, each of which contains (x, y) threads.

the multiprocessors (e.g. block widths should most often be a multiple of 16 to allow for coalesced global memory).

When a CUDA application is executed, each block is assigned to execute on one multiprocessor. This multiprocessor will manage and execute the threads within the block on its SPs. While the block arrangement does not have a significant impact on the execution of the threads on the multiprocessors, it strongly affects the manner in which threads access memory and use the memory optimisations available on the GPU. Threads should be arranged into blocks such that the maximum amount of data can be shared between threads in shared/texture/constant memory and that any unavoidable global memory accesses be coalesced.

#### 2.2.4 Multi-GPU

While GPUs are computationally powerful, many problems are so large that we wish to compute them on more than one GPU. Each GPU performs its own thread management automatically in hardware. This management is restricted to the individual GPUs, thus additional management is required when splitting an application across multiple GPUs. CPU level code is required to decompose tasks across multiple GPUs and deal with the challenges of data communication, and synchronisation.

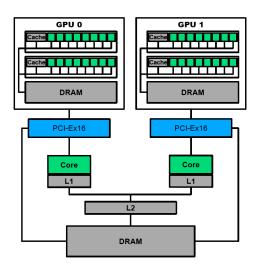

Many motherboards have several PCI-E x16 slots and are thus capable of hosting multiple GPU devices. Some graphics cards such as the GeForce GTX 295 or the GeForce 9800 GX2 contain two GPU cores on a single graphics card. In such configurations, multiple threads are required to interact with the GPU devices. While single-core machines are capable of managing multiple threads interacting with multiple GPUs, it is obviously advantageous to have as many CPU cores as there are GPU devices. Figure 5 shows a multi-GPU configuration with a dual-core CPU controlling two GPUs on separate PCI-E x16 slots.

Communicating data between CPU threads controlling GPU devices is not as simple as communication between threads. CPU processor cores share memory and L2 cache and simply have their own L1 cache (See Figure 2). Data that needs to be communicated between CPU threads can be performed simply by writing to memory, synchronising and then reading. This is not quite as simple when communicating data between multiple GPUs. The CPU threads can communicate information as usual but it requires that the data first be retrieved from the GPU device, exchanged and then written back into the appropriate device.

These systems encounter the usual problem of communication versus computation time. For multiple GPUs to be used efficiently, the time taken to perform the computation should be significantly larger than the time required to communicate the necessary data between them. For multi-GPU systems, this requires very large problem sizes as each GPU is in itself a powerful,

Figure 5: A multi-GPU machine containing two GPUs each hosted on separate PCI-E x16 buses and managed by separate CPU cores.

highly-parallel computer. The best method for improving this communication to computation ratio is obviously dependent on the problem; however, CUDA does provide a very useful piece of functionality that can be useful for many applications.

CUDA has support for asynchronous execution and data-transfer [46]. This type of execution can allow the GPU to execute threads while at the same time the CPU can transfer data in and out of the GPU device. Using this functionality can allow the communication to be performed at the same time as the computation which, in the right conditions, can allow the effective communication time be reduced to zero. Using this functionality has been shown to make the use of multiple GPU devices scale effectively (See Section 4.9).

Such Multi-GPU machines have been shown to produce good scalability for a variety of problems such as saliency map models [50], RNA folding algorithms [51] and Smith-Waterman sequence alignment [52] etc. The scalability of Multi-GPU machines is limited by the number of GPUs that can be hosted on a single machine. Some motherboards are capable of hosting up to four graphics cards which could potentially contain two GPU cores, limiting the maximum number of GPUs on a single machine to eight.

Such machines would require large power supplies but it is still worth considering. How well an application can be divided across eight GPU cores is, as always, dependent on the application. If no communication between the GPUs is necessary, then we can expect a near linear speedup, however as the communication between the GPUs increases we expect the speedup to decay. In these situations optimal use of functions such as asynchronous memory copy and execution is vital to attaining good scalability across the multiple GPU cores.

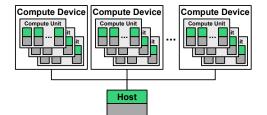

#### 2.2.5 GPU-Accelerated Clusters

Another option for multi-GPU computation is to host the GPUs on multiple nodes spread across a cluster or other distributed device. These GPUs then take the form of accelerators for the individual nodes on the cluster. GPU accelerated clusters simply combine two technologies, the relatively new GPGPU libraries and the well-developed distributed computing frameworks such as MPI [36]. GPU clusters with promising scaling results have been described for a number of applications - Finite Differencing [53], Biomedical Analysis [54], lattice Boltzmann model [55], Fluid Dynamics [56].

The CPU cores in these cluster nodes perform inter-node communication using common cluster

Figure 6: A diagram showing a GPU cluster configuration containing N GPU-accelerated nodes. In this cluster each node contains a single GPU.

communication methods such as MPI [36] and use a GPGPU library such as CUDA [46] to perform calculations on the GPU. The nodes on these clusters are not limited to a single GPU and can in fact consist of a distributed architecture of multi-GPU nodes. In such cases there is communication between the GPUs in the same node via the host memory and inter-node communication across the cluster communication network.

Such GPU-accelerated clusters face more challenges in terms of achieving a high computationto-communication ratio. While the GPUs can be utilised to accelerate the nodes of the cluster to reduce computation time, they can provide little benefit in terms of improving the inter-node communication speeds. This issue has been documented by GPU cluster developers [57]. The GPUs do not reduce the performance of the cluster and are almost always successful in accelerating it [55– 57]; however, the limitations of the node communication infrastructure become more apparent.

Like multi-GPU machines, GPU-accelerated clusters can make use of CUDA's asynchronous memory copies and execution to perform communication while the GPU continues to perform calculations. This can be used effectively with MPI's asynchronous Send/Recv to communicate data between GPUs on the same node and between nodes in the cluster without the GPUs being left idle.

### 2.3 Cell Broadband Engine

The consortium of Sony, Toshiba and IBM (STI) produced a multi-core processor chip that is known as the Cell Broadband Engine (CellBE) [58] and which is now widely known as the processor in the Sony PlayStation 3 (PS3) games machine. The CellBE comprises a PowerPC processing core (PPE) but is unusual in that it is supported by eight "synergistic processing elements" (SPEs) that provide additional performance acceleration [59]. A number of other products now have processors based on the PPE component of the CellBE including the Microsoft Xbox 360 games engine, and the CellBE itself is also available in blade systems. The CellBE design was apparently driven by silicon space and also power consumption considerations [60], and this design paradigm – of a relatively conventional main core supported by specialist processing accelerator cores – may become more prevalent as chip vendors attempt to combine large numbers of cores with other design criteria like minimal power consumption.

The CellBE as supplied on the Sony PlayStation 3 is accessible to a Linux programmer through

the STI software development kit and a compilation system based on the Free Software Foundation GNU gcc compiler [61]. Scarpino's book [59] describes how to program the CellBE on the PS3 in more detail, but in brief it is possible to program both the PPE and the SPE using appropriate libraries called from what are essentially C/C++ application programs. The PS3 implementation uses a hypervisor arrangement so the Gaming Operating system supplied by Sony supervises a running Linux, but only six of the available eight SPEs are exposed to the Linux programmer. Similarly some additional features of the CellBE such as the graphics and storage interface are not directly controllable.

Nevertheless, the PS3/CellBE/Linux combination provides a remarkably cost effective developmental platform for development of application programs for the CellBE and has allowed us to investigate some of the relevant features for comparison with the other software and hardware platforms discussed in this article.

As Dongarra and others have reported [62,63], the PS3 is an appropriate platform for some but not all scientific applications. Although it is possible to use the PS3 network interface to cluster multiple PlayStations together, in this present paper we report only on performance observations using a single CellBE in a single PS3. Our main observation is that, at least at the time of writing, some considerable expertise, time and effort is required on the part of the applications programmer to make full use of the processing power of the CellBE. In fairness this is true of parallel programming generally. If programmer use of parallelism is necessary to attain optimal performance on future processors that have of necessity been designed to have low power considerations, then better software tools and/or programmer expertise will be required.

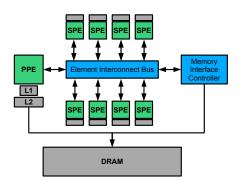

Figure 7: Cell Processor Architecture with eight SPEs. The PPE and SPEs can communicate via the Element Interconnect Bus. The SPEs access memory via the Memory Interface Controller.

Figure 7 summarises the main points of the CellBE architecture. The PPE unit has some common ancestry with IBMs's other PowerPC chip designs and is a powerful core in its own right. It is supported by eight SPE cores each of which has some dedicated memory (256kB) and which are accessible through a bi-directional dual ring interface. The software development kit and associated library provide a great many library calls to communicate between different core components of the CellBE. Mechanisms include mailboxing and signalling as well as bulk data transfers using a Direct Memory Access (DMA) support infrastructure.

Generally, it is not difficult for an applications programmer to develop a master/slave software model to delegate computations to the SPE from the PPE. A Monte Carlo example for instance works well, providing that tasks for the slave SPE's fit in their own memory. Otherwise, some care in needed to barrier-synchronise their access to global memory to avoid contentions.

A number of software packages are relatively trivially ported to work on the PPE main core, treating it as any other PPC instructions set architecture. For example the Erlang parallel language system [41] worked on the PPE trivially. As a very rough indicator, we found the PPE by itself gave a performance equivalent to around half of that of a single CPU core on a contemporary desktop.

This is quite impressive given the CellBE was designed with completely different optimisation criteria. To obtain high performance from the CellBE it is necessary to a) delegate computational work to the SPEs and b) make use of the vector instructions on both the PPE and SPEs.

The PPE and SPEs are capable of processing vector data types performing four instructions synchronously. To make full use of the SPEs, the programmer must use spu\_add, spu\_mul, etc to transform calculations into vector form. Other performance optimisation techniques available are enqueued DMA access (IE fetch memory while computing); bi-directional use of the IE ring; use of the memory flow controller.

#### 2.4 Other Accelerator Hardware Approaches

Another approach to gaining applications performance involves field programmable gate arrays (FPGAs) [64]. These reconfigurable devices can be programmed at a very low level for arbitrary logical operations and can thus perform specific and particular applications algorithms at high speeds. Modern FPGA devices operate around power dissipation levels of around 25 watts compared with levels around 60-70 for heterogeneous core devices like the CellBE or in excess of 100 watts for conventional monolithic multi-core processors.

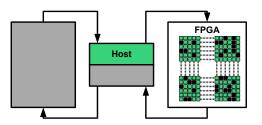

Figure 8: A host device utilising an FPGA to accelerate specific calculations.

Figure 8 shows the block outline of an FPGA program as it might be used to accelerate a particular operation such as an image processing kernel or a Fourier Transform. A modern FPGA is typically programmed using design tools that can draw on libraries of the low level logic pattern – effectively small processing cores – that can perform a particular algorithmic aspect of an application. FPGAs tend not perform well with non-floating point calculations or with less general specific operations. As affordable FPGAs become larger and have larger number of primitive gates available however, it is likely that general purpose floating point cores may be readily embeddable in FPGA program designs.

FPGAs have traditionally been used for signal and image processing applications but have been more recently successfully used for financial simulations and calculations [65]. Although their power characteristics, and performance/cost ratios are potentially very attractive, the main obstacle to wider applications deployment of FPGAs lies in the difficulties (and hence costs) of programming them at an applications level. Other issues facing applications developers include the considerable variation in the data-types and bit-lengths of operating words and buses for different FPGAs and families of devices. Some portability for applications codes is likely needed to lower the cost of FPGA software development.

Vendor specific languages such as Mitrion-C [66] and its associated toolset provide a potential route for applications programmers to develop relatively high level applications programs that can be automatically decomposed into VHDL logic patterns for programming FPGAs. Mitron supply a Turing-complete library of predesigned processing core components that can be combined to support applications. This approach of writing applications programs that can be used as a hardware independent "device middleware" is a promising one. We speculate that languages such as OpenCL may play a similar role for other compute devices in the future.

We have attempted to review the main classes of accelerator devices and their characteristics. We have not covered all vendors and have necessarily been restricted by our own time and hardware budgets. AMD and other vendors also produce powerful and attractive multi-core processors. The Jaguar Supercomputer [39] at the Oak Ridge National Laboratory in the USA is based around over 180,000 AMD Opteron processing cores.

Other systems such as the the Roadrunner Supercomputer [38] at the Los Alamos Laboratory in the USA is based around use a hybrid of different multi-core processors including IBM PowerPC designs similar to the CellBE heterogeneous design. There are also a number of new devices forthcoming such as Intel's Larrabee and AMD's Fusion multi-core processors that may have different optimisation characteristics than those discussed below. We discuss the CellBE as it was accessible to us within Sony PlayStation 3's, but it is also possible to obtain specialist accelerator devices based around this processor, without the six SPE restrictions. We discuss the SIMD and array-processing aspects of NVIDIA's GPUs but devices such as ClearSpeed [67] which are based around a multi-threaded array processor (MTAP) approach also find uses as specialist accelerators in a range of different compute systems and applications [68, 69].

The future of accelerated processing units is likely to prosper, albeit with the expected continued push to incorporate the successful cores or accelerator designs on to future multi-core designs that are better integrated. It is still non-trivial to compare the available groups of accelerator devices without focussing on specific implementation and performance measurement details. We attempt this in the next sections.

## **3** Performance Experiments

We provide a comparison between the different accelerator devices we have discussed by presenting the implementation of several scientific applications on each device and comparing their results. The scientific applications we have chosen as representative of most scientific applications are: Finite Differencing (Section 4), Graph Clustering (Section 5) and Random Number Generation (Section 6).

Finite differencing algorithms operate on the cells of a regular mesh. This regularity makes them particularly well suited for SIMD architectures. Furthermore, data dependencies exist between neighbouring cells, which means that hardware support for spatial locality in the data, for example texture memory in CUDA devices, is very beneficial.

Algorithms that iterate over arbitrary graphs, on the other hand, do not benefit as much from SIMD architectures and spatial locality in the data, as the graph structure is not known beforehand. But with the right data layout and access strategies, they can nevertheless perform well even on these kinds of accelerators.

After these two somewhat opposing scenarios are covered, we look at one of the most widely used facilities in scientific simulations, namely random number generation. A parallel scientific application often uses a separate stream of random numbers for each thread in order to ensure that the simulation is repeatable. This is exactly what most of the implementations described in this article do as well. Another advantage is that independent generators do not introduce communication overhead between the threads.

The platform we have used for all performance experiments except for the CellBE algorithms runs the Linux distribution Kubuntu 9.04 64-bit. It uses an Intel® Core<sup>TM</sup>2 Quad CPU running at 2.66GHz with 8GB of DDR2-800 system memory and an NVIDIA® GeForce® GTX 295 graphics card, which has 2 GPUs with 896MB of global memory each on board.

The platform used to run the CellBE implementations is a PlayStation®3 running Yellow Dog Linux 6.1. It uses a Cell processor running at 3.2GHz, which consists of 1 PowerPC Processor Element and 8 Synergistic Processor Elements, 6 of which are available to the developer. It has 256MB of system memory.

In view of the importance of presenting coding details but also trying to bring out compar-

isons between the different architectures and devices and software, we give algorithms in stylised pseudo-code with device-specific software library calls embedded in them. We believe this makes it easier to compare different device implementations than either verbatim program code or a terser mathematical notation would be.

## 4 Finite Differencing

Finite differencing methods can be used to numerically approximate solutions to n-dimensional systems described by a partial differential equation. They approximate the continuous space of some physical or mathematical system by a mesh of discrete cells. Sub-categories of finite differencing applications include field-equations and image processing (physical space is approximated by the camera as a mesh of pixels). Finite differencing applications perform many regular, local operations on the cells in the mesh.

These applications are easy to decompose for execution on parallel accelerator devices. The mesh can be split into sections and each one processed separately. This mesh separation can take a very coarse form (split the field into two for execution on two processors) right down to a very fine-grained decomposition (each section is one cell). The regular instructions and memory access patterns make them good candidates for many optimisations available on accelerator devices.

### 4.1 Neighbour Operations

The operations of finite differencing problems usually perform some calculation on how to change the value in the cell depending on the values of the cells surrounding it (the neighbouring values that must be accessed are called the memory halo of the problem). In general, more complex equations that require accesses to more neighbours will have slower simulation times due to the extra memory fetches and calculations. Figure 9 shows some common memory halos used by various finite differencing applications.

|  |  | ] |  |  |  |  |  |  |

|--|--|---|--|--|--|--|--|--|

|  |  | 1 |  |  |  |  |  |  |

|  |  | 1 |  |  |  |  |  |  |

|  |  |   |  |  |  |  |  |  |

|  |  | 1 |  |  |  |  |  |  |

Figure 9: Some common memory halos used by finite-differencing applications.

This is especially true for accelerator devices such as GPUs. For devices with specific memory caches with limited sizes, the memory halo can have a large impact on performance. If the values required by neighbouring threads on a GPU cannot fit within the caches, cache thrashing can occur which may severely reduce performance.

The memory halo also has a significant impact on the parallelisation of a finite differencing problem. This halo determines the amount of communication required by nodes responsible for neighbouring sections of the field. A larger memory halo will mean less cells can be processed between communications and more data must be transfered between nodes. Simulations with large memory halos will parallelise less easily, as there is no way to reduce this memory halo this issue cannot be resolved but it is important to consider it in simulation design as different parallelisation methods may suit different halo sizes.

### 4.2 CPU - Sequential Algorithm

The most basic finite-differencing simulation is implemented on one core of a CPU. This application iterates through each cell in the mesh calculating the change in the value of the cell and writing

it to some output mesh. In this example we call the function update for each element in the mesh, the actual calculation and neighbouring cells accessed will depend on the finite-differencing equation being applied to the mesh. Algorithm 1 shows the CPU algorithm for iterating over a two-dimensional mesh.

**Algorithm 1** Pseudo-code for the serial CPU implementation of the Finite Differencing Simulation. Computes some update function for a field of size (X, Y) over *no\_steps* iterations.

```

declare input

declare output

initialise(input)

for t \leftarrow 0 to no_steps do

for y \leftarrow 0 to Y do

for x \leftarrow 0 to X do

update(input, output, x, y)

end for

swap(input, output)

end for

```

The update function will read in the cell at position (ix,iy) and the required neighbouring values from the mesh input, calculate the new value of the cell and then write it into the mesh output. At the end of each step, the input and output meshes are swapped, the output from the last time-step becomes the input for the next and so on.

While the update function is equation specific, the code to iterate over the mesh will remain the same for almost all finite differencing simulations. This simulation is expected to be the slowest implementation as it only uses a single CPU core. We can accelerate this simulation by using multiple cores or accelerator devices.

### 4.3 Multi-Core: POSIX Threads

To compute a finite-differencing simulation on multiple cores we must make use of a multi-threading library to create and manage multiple threads. The most basic option is the well known POSIX thread library [43]. This library allows the developer to explicitly create, destroy and synchronise threads with the use of mutexes.

As this is a relatively low-level threading library it requires the developer to consider and explicitly define the behaviour of each thread including problem decomposition, task distribution, communication and synchronisation. This results in a rather longer development time and can be more prone to inconsistencies (especially with more complex simulations). The advantage of such a low-level library is that developer can make low-level tuning to extract the highest-performance possible.

The pseudo-code describing the algorithm of the main thread is shown in Algorithm 2 and the algorithm each of the threads performs is described in Algorithm 3.

The separate threads each execute process\_block which will wait for the mutex start to be unlocked. It will then process a section of the field and unlock the mutex stop. The iterative loop in the main thread will loop no\_steps times unlocking mutex start for each thread and then wait until all threads have unlocked stop. This ensures that the threads remain in sync and the field will be properly updated.

### 4.4 Multi-Core: Threading Building Blocks

Intel's Threading Building Blocks (TBB) can reduce the development time and improve the reliability of multi-threaded applications by abstracting common multi-threaded functions into the

```

Algorithm 2 Pseudo-code for the host code for the PThreads implementation of the finite-

differencing simulation. Each thread launched will execute the function process_block, see Algo-

rithm 3

```

```

declare input

declare output

declare THREADS \leftarrow \{t_0, t_1 \dots t_{n-1}\}

initialise(input)

for all t_i \in THREADS do

create(process_block, t_i)

end for

for t \leftarrow 0 to no\_steps do

for all t_i \in THREADS do

signal start(t_i)

end for

for all t_i \in THREADS do

wait stop(t_i)

end for

swap(input, output)

end for

```

Algorithm 3 Pseudo-code for the algorithm performed by each thread in the PThreads implementation of the finite-differencing simulation.

```

function process_block(id)

while TRUE do

wait start(t_{id})

height \leftarrow Y/n

for y \leftarrow id \times height to ((id + 1) \times height) do

for x \leftarrow 0 to X do

update(input, output, x, y)

end for

signal stop(t_{id})

end while

end function

```

library itself. This can improve the development time of many parallel applications that can make use of these constructs. In this case we wish to iterate over a mesh and apply the field equation function to every element in the mesh. For this we can use TBB's **parallel\_for** function which will split the task of iterating over the mesh across the cores available in the CPU.

The range of the mesh to be iterated over in parallel is defined by a TBB construct **blocked\_range2d**. This specifies a X and Y range as well as a grain size for decomposition. The X and Y grain sizes specify the size of the blocks that the mesh will be decomposed into. This allows the user to control how finely grained the parallelism is. Algorithm 4 and Algorithm 5 show the code for TBB that iterates over a mesh in parallel. In this case the grain sizes specify that the mesh should be divided into 64x64 blocks of cells.

**Algorithm 4** Pseudo-code for the host code of the TBB implementation of the finite-differencing simulation.

| declare input                                           |

|---------------------------------------------------------|

| declare <i>output</i>                                   |

| <b>declare</b> blocked_range2d $br(0, Y, 64, 0, X, 64)$ |

| initialise( <i>input</i> )                              |

| for $t \leftarrow 0$ to no_steps do                     |

| $parallel_for(br, update)$                              |

| swap(input, output)                                     |

| end for                                                 |

Algorithm 5 The update function used by the TBB implementation of the finite-differencing simulation.

function update(blocked\_range2d br) declare  $y\_begin \leftarrow br.rows().begin()$ declare  $y\_end \leftarrow br.rows().end()$ declare  $x\_begin \leftarrow br.cols().begin()$ declare  $x\_end \leftarrow br.cols().$  end() for  $y \leftarrow y\_begin$  to  $y\_end$  do for  $x \leftarrow x\_begin$  to  $x\_end$  do update(input, output, x, y) end for end for end function

### 4.5 GPU - CUDA

These applications are very well suited to GPU processing, GPUs were originally designed for generating computer graphics images. As finite-differencing meshes are very similar to images, and may in-fact be images, finite-differencing applications can make effective use of many of the optimisations available on the GPU.

When executing a finite-differencing application on a GPU, one thread is created for every cell in the mesh. This task decomposition method is similar to the parallel\_for concept in TBB except that each thread is only responsible for a single cell (effectively a grain size of 1). Because GPU architectures are designed for managing, scheduling and executing thousands of threads on hardware, the program does not suffer any thread management overhead from such fine-grained parallelism.

Each thread will calculate the position of its element in the mesh from the thread's block and thread id. It can then access this cell's value and the values of the necessary neighbouring cells,

compute the new value of the cell and write it to some output mesh. Algorithm 6 shows a CUDA simulation that launches  $X \times Y$  threads organised into (16,16) blocks. This block size provides a square shape for best caching effects, a width of 16 to allow coalesced global memory access and fits within the restriction 512 threads maximum per block.

Algorithm 6 Pseudo-code for the host portion of the CUDA implementation. One thread is created for each cell in the mesh and will perform the update calculation for that cell.

| declare $block(16,16);$                           |

|---------------------------------------------------|

| declare $grid(X/block.x, Y/block.y)$              |

| declare texture                                   |

| declare input                                     |

| declare <i>output</i>                             |

| initialise(input)                                 |

| $\mathbf{copy} \ texture \leftarrow input$        |

| for $t \leftarrow 0$ to <i>no_steps</i> do        |

| do in parallel on the device using (grid, block): |

| <b>call</b> update( $output$ )                    |

| $\mathbf{copy} \ texture \leftarrow output$       |

| end for                                           |

For the best performance, this implementation makes use of CUDA texture memory. This texture memory cache is very effective for applications performing local neighbour operations as it automatically caches values in the same spatial locality. This has been shown to provide the best performance for field equation simulations [70].

### 4.6 Multi-GPU - CUDA & POSIX Threads

The multi-GPU implementation is the most complex of our finite differencing simulations, this is due to the several levels of parallelism within the simulation. For ease of description we discuss a dual-GPU implementation, however the same concepts can easily applied to systems containing more GPUs. The first level of parallelism is splitting the field across multiple cores on the GPU. In this case we have two-GPUs so we split the field into two sections.

One thread is created for each section. These two threads will connect to one GPU each and compute the interactions of the cells in their half of the field. This computation is performed in parallel on the GPU (the second level of parallelism).

The cells on the border of each half-field must access cells from the other half-field to correctly calculate their change in value. Thus after each time-step the threads must communicate a border of cells to the other device. The width of this border depends on the memory halo of the finite-differencing equation. In this case we discuss an equation with a border of width 2.

The field is split in the y-dimension as this allows each field segment to be stored in contiguous memory addresses. This provides advantages when copying border information as it is faster to copy 2 segments of memory with 2x elements (the top and bottom borders each contain 2x elements) than copying 2y segments containing 2 elements.

One way to do this communication is to: compute the simulation for the entire half-field, stop, retrieve the bordering cells from the GPU, exchange these cells with the other thread and then continue. While this method would work, it leaves the GPU idle while the cells are retrieved from the device and exchanged between the threads. This is valuable computing resources going to waste.

A solution to this is to make use of asynchronous execution. Instead of computing the simulation all at once, we can launch two separate asynchronous kernels. The first computes the cells on the border (a small fraction of the total half-field size) while the other computes all of the other cells. As the first kernel will complete before the second (there are less cells in the border than in the main body of the field), we can asynchronously copy the border cells out of the device and exchange them with the other thread while the main GPU kernel is still executing. When the second main kernel call finishes, the communication of the border cells is already complete and the next step can be started immediately. This allows us to hide the communication time and make the maximum use of the GPU computing resources.

For this implementation we have made use of POSIX threads for managing the multi-threading. Textures in CUDA must be referenced explicitly within the code, this requires the threads to initialise, load and use the same texture reference throughout the simulation. This application can be implemented using TBB threads, it would be effectively the same just with TBB syntax as opposed to PThreads syntax. The algorithm for the host thread can be seen in Algorithm 7 and the code for each thread can be seen in Algorithm 8.

**Algorithm 7** Pseudo-code for the host algorithm for the PThreads & CUDA multi-GPU implementation of the finite-differencing simulation.

```

declare input

declare output

declare THREADS \leftarrow \{t_0, t_1 \dots t_{n-1}\}

for all t_i \in THREADS do

create(process, t_i)

end for

for t \leftarrow 0 to no_steps do

for all t_i \in THREADS do

signal start(t_i)

end for

for all t_i \in THREADS do

wait stop(t_i)

end for

end for

end for

```

This implementation can provide a 2x (linear) speedup over a single GPU implementation provided that the problem is large enough that the communication time is less than is required for the main kernel call. A field length of  $N \ge 2048$  can make full use of both GPUs. For field sizes less than this, the multi-GPU simulation may run slower than a single GPU implementation as the communication between the two devices can take longer than the actual computation. This effect can be seen in Figure 10.

### 4.7 OpenCL

The currently available OpenCL implementations we have developed finite differencing simulations on are still pre-beta releases and thus we do not present performance data on their computational speed. We do however include a code example showing how the program iteratively computes simulation steps.

As OpenCL is device independent, the optimal sizes of local (which defines the grain size) should be set differently depending on the device. OpenCL running on a GPU will perform best with a grain size of 1 while larger sizes similar to those used by TBB will provide the best performance for multi-core CPUs. The code to iteratively call an OpenCL kernel on a field of size (X,Y) with grain size 16 can be seen in Algorithm 9.

OpenCL does not work with one single type of device and when writing code it is not known what type of device will be used to execute the code (although certain types of device can be requested). When the OpenCL application executes, it queries the machine to find OpenCL compatible devices that it can use. In the pseudo-code this is shown as get\_context(), which will load a context on a OpenCL compatible device that it will use to execute the application.

```

Algorithm 8 Pseudo-code for the thread algorithm for the PThreads & CUDA multi-GPU implementation of the finite-differencing simulation. Calling update(stream, output, Y) will launch a kernel in an asynchronous stream stream, writing data to output starting from row Y.

```

```

function process(size_t id)

declare id2 \leftarrow other thread's id

copy texture \leftarrow input

while TRUE do

wait start(t_{id})

declare block(16, 16)

declare grid(X/block.x, 1)

do in parallel on the device using (grid, block):

call update(stream1, output, 2)

do in parallel on the device using (grid, block):

call update(stream1, output, Y2 + 2 - block.y)

grid \leftarrow (X/block.x, Y-4)

do in parallel on the device using (grid, block):

call update(stream2, output, 2 + block.y)

synchronize (stream1)

copy swap[id2][0] \leftarrow output[2 \times X], 2 \times X

copy swap[id2][2 \times X] \leftarrow output[Y2 \times X], 2 \times X

signal copy(t_{id2})

wait copy(t_{id})

copy output[(Y2+2) * X] \leftarrow swap[id][0], 2 \times X

copy output[0] \leftarrow swap[id][2 \times X], 2 \times X

synchronize (stream2)

copy texture \leftarrow output

signal stop(t_{id})

end while

end function

```

| Algorithm 9 Pseudo-code for an OpenCL finite-differencing implementation. |

|---------------------------------------------------------------------------|

| declare $local \leftarrow \{16, 16\}$                                     |

| <b>declare</b> $global \leftarrow \{X, Y\}$                               |

| declare context                                                           |

| declare kernel                                                            |

| $context \leftarrow get\_context()$                                       |

| $kernel \leftarrow load_kernel()$                                         |

| for $n \leftarrow 0$ to no_threads do                                     |

| set kernel argument(kernel, 0, input)                                     |

| set kernel argument(kernel, 1, output)                                    |

| do in parallel on the device using (global, local):                       |

| call kernel (context, kernel)                                             |

| end for                                                                   |

While our OpenCL implementation of the finite-differencing simulation does run and produce correct results, we have chosen not to present performance results for this implementation. This is due to the fact that the OpenCL implementation used is still in a pre-release stage and some optimisations do not correctly function. Thus we feel that it would be unfair to compare its performance to the other implementations.

### 4.8 Cell Processor - PS3

The PS3 implementation of the simulation is designed to make use of the vector processing abilities of the SPEs and the queued memory access. The PPE itself acts as a synchronisation and control unit for the SPEs which perform the actual processing. The PPE uses the mailbox system to communicate with the SPEs and ensure that they remain in sync. As the SPEs and PPE can access the same memory space there is no need for data transfer, simply correct synchronisation. The code to create the threads executing on the SPEs and to communicate with them via mailbox is shown in Algorithm 10.

Algorithm 10 Pseudo-code for an CellBE finite-differencing implementation.

```

declare SPE \leftarrow \{spe_0, spe_1, \dots, spe_5\}

for all spe_i \in SPE do

spe_i = spe\_create\_thread(update, input)

end for

for t = 0 to no\_steps do

for all spe_i \in SPE do

write to inbox(spe_i)

end for

for all spe_i \in SPE do

read from outbox(spe_i)

end for

end for

```

In this simulation the field is defined as an array of type vector float. This allows the SPEs to load values and compute the simulation using vector operations (allows four scalar operations to be performed as a single instruction). This effectively processes four cells in the simulation at once.

To improve performance the simulation makes use of enqueued memory access. Initially each SPE will load the vectors required to compute the simulation for the next 16 vectors. Before processing these values, the extra vectors required for the next 16 vectors are enqueued to be fetched. As the memory fetching can be performed asynchronously with the SPE execution, the SPE can compute the simulation for a set of vectors while the values required for the next set are being fetched. This reduces the time the SPE must wait for the memory to be fetched and greatly improves the performance of the simulation.

One challenge with using vector operations is correctly calculating the neighbours. As each element in the vector is a different cell in the simulation, each element's neighbours must be fetched. This is not as simple as fetching the neighbouring vector as this will be the vector neighbour rather than the element neighbour. Instead vectors containing the element neighbours must be generated using suitable insert, extract and rotate methods. See Algorithm 11.

### 4.9 Finite Difference Results

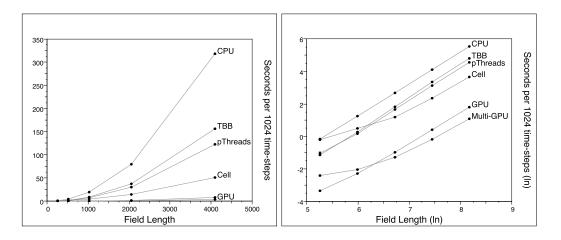

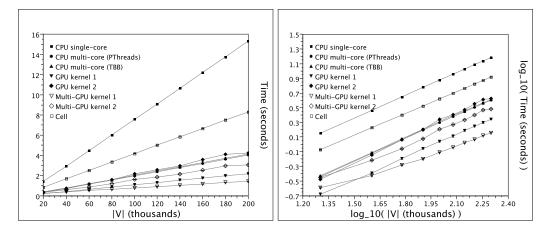

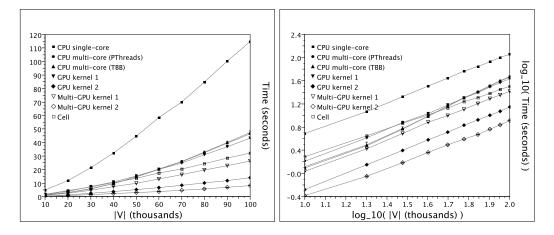

To test and compare these different implementations, we measured the average computation-time per 1024 simulation time-steps. These results, presented in Figure 10, have been gathered for multiple field lengths to compare the performance across multiple mesh sizes.

Algorithm 11 Pseudo-code for accessing neighbours using vectors on an SPE. This algorithm only fetches the four direct neighbours of a cell.

declare vector float  $above \leftarrow input[y-1][x]$ declare vector float  $cell \leftarrow input[y][x]$ declare vector float  $below \leftarrow input[y+1][x]$ declare vector float leftdeclare vector float rightdeclare float temp $temp \leftarrow extract(input[iy][x-1], 3)$  $left \leftarrow rotate\_right(vyx)$  $left \leftarrow insert(temp, left, 0)$  $temp \leftarrow extract(input[iy][x+1], 0)$  $right \leftarrow rotate\_left(vyx)$  $right \leftarrow insert(temp, right, 3)$

Figure 10: A performance comparison of the finite-differencing results implemented on several devices, shown in normal scale on the left and ln-ln scale on the right. Please note that these graphs do have error bars, however they are all smaller that the points on the graph.

As expected, the single CPU implementation provides the worst performance but provides a meaningful baseline for comparing the other devices. The POSIX threads and Threading Building Blocks implementations provide similar performance, the TBB implementation is the slower of the two.

The simulation running on the CellBE device produced the same results over twice as fast as the PThreads implementation for system sizes of N > 1024. System sizes below this were not large enough to make use of the CellBE capabilities.

The GPU implementations provided the best performance running many times faster than the CPU implementation. For a system size of  $N \ge 2048$  the Multi-GPU version can provide an almost linear (2x) speedup over the single GPU implementation. However, for system sizes any smaller than this, the performance degrades significantly and can take longer to compute the simulation than the single-GPU implementation. This is caused by the need to communicate the values of the border cells through CPU memory. For small system sizes, this communication takes longer than the actual computation and thus the use of multiple GPU devices slows the simulation.

## 5 Newman's Clustering Coefficient

This section describes how various parallel architectures and toolkits can be used to parallelise Newman's clustering coefficient [71]. This graph metric is based on the concept of clustering in social networks, sometimes also called network transitivity, introduced by Watts and Strogatz [72]. It is commonly used when analysing networks with small-world characteristics [72–74].

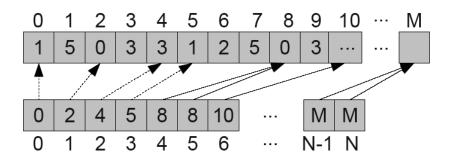

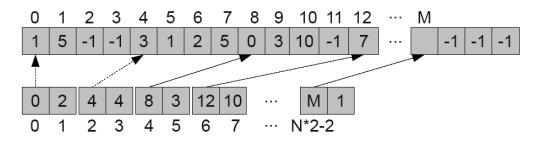

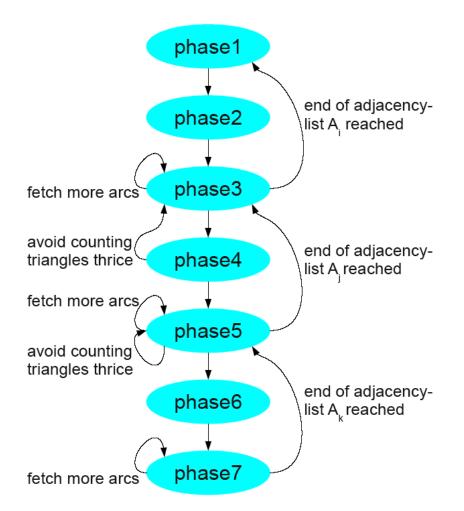

## 5.1 CPU - Sequential Algorithm

Algorithm 12 Pseudo-code for the sequential CPU implementation of the clustering coefficient. function CLUSTERING(G)

```

Input parameters: The graph G := (V, A) is an array of adjacency-lists, one for every vertex

v \in V. The arc set A_i \subseteq A of a vertex v_i is stored in position V[i]. |V| is the number of vertices

in G and |A_i| is the number of neighbours of v_i (i.e. its degree).

R \leftarrow determine reverse adjacency-list lengths

declare t //triangle counter

declare p //paths counter

for all v_i \in V do

for all v_i \in A_i do

if v_i = v_i then

p \leftarrow p - R[v_i] //\text{correct for self-arcs}

continue with next neighbour v_{i+1}

end if

p \leftarrow p + |A_j|

if v_i > v_j then

for all v_k \in A_j do

if v_k = v_i then

p \leftarrow p - 2 //correct for cycles of length 2 for both v_i and v_j

continue with next neighbour v_{k+1}

end if

if v_k \neq v_i AND v_i > v_k then

for all v_l \in A_k do

if v_l = v_i then

t \leftarrow t + 1

end if

end for

end if

end for

end if

end for

end for

return (3t)/p //the clustering coefficient

```

Algorithm 12 illustrates how the clustering coefficient is calculated. It is defined as:

$C = \frac{3 \times (\text{number of triangles on the graph})}{\text{number of connected triples of vertices}}$

Here triangles are elementary circuits of length three (i.e. three distinct vertices connected by three arcs creating a cycle). A connected triple is a path of length two (i.e. two arcs) that connects three distinct vertices.

### 5.2 Multi-Core: POSIX Threads

The outermost loop of the sequential implementation executes once for every vertex  $v_i \in V$ . The iterations do not interfere with each other and can thus be executed in parallel. It is merely necessary to sum up the numbers of triangles and paths found in each of the parallel iterations to get the total counts for the graph before the clustering coefficient can be calculated. Algorithms 13 and 14 describe an implementation that uses POSIX Threads (PThreads) to achieve parallelism.

Algorithm 13 Pseudo-code for the multi-core CPU implementation of the clustering coefficient using POSIX Threads. See Algorithm 12 for a description of the input parameter G and the actual triangle and paths counting algorithm.

```

declare v_{curr} //the current vertex

declare mutex m //mutual exclusion for v_{curr}

function CLUSTERING(G)

R \leftarrow determine reverse adjacency-list lengths

v_{curr} \leftarrow 0 //initialise current vertex v_{curr}

n \leftarrow numer of CPU cores

do in parallel using n threads: call PROCESS(G, R)

wait for all threads to finish processing

declare t \leftarrow sum of triangles found by threads

declare p \leftarrow sum of paths found by threads

return (3t)/p //the clustering coefficient

```

### Algorithm 14 Algorithm 13 continued. The function *PROCESS* is executed in parallel.

```

function PROCESS(G, R)

declare t //local triangle counter

declare p //local paths counter

declare v_s //start vertex

declare v_e //end vertex

repeat

acquire lock on mutex m

v_s \leftarrow v_{curr}

v_e \leftarrow v_s + \text{ work block size } / / v_e \text{ must not exceed } |V|

v_{curr} \leftarrow v_e

release lock on mutex m

for all v_i \in V_i \equiv \{v_s, \ldots, v_e\} \subseteq V do

count triangles and paths as described in the sequential CPU implementation

end for

until v_s \geq |V|

return \{t, p\}

```

### 5.3 Multi-Core: Threading Building Blocks

The TBB implementation, like the PThreads version explained before, applies the parallelism to the outermost loop. TBB's parallel\_reduce can be used to do this parallel reduction without having to explicitly specify the chunk size and number of threads or having to worry about keeping all the threads busy.

Algorithm 15 shows how the full iteration range is defined and passed to parallel\_reduce. TBB recursively splits the iteration range into sub-ranges until a certain threshold is reached. Then

TBB uses available worker threads to execute PROCESS\_TASK (Algorithm 16) in parallel. When the two halves of a range have been processed, then TBB invokes function JOIN (Algorithm 17) to combine the results. Eventually, all sub-ranges have been processed and the results have been joined into the root of the task tree. TBB returns and the results can be extracted from this root object.

Algorithm 15 Pseudo-code for the multi-core CPU implementation of the clustering coefficient using TBB. See Algorithm 12 for a description of the input parameter G and the actual triangle and paths counting algorithm.

function CLUSTERING(G)  $R \leftarrow$  determine reverse adjacency-list lengths declare blocked\_range br(0, |V|)call parallel\_reduce(br, PROCESS\_TASK) retrieve results and calculate clustering coefficient